本篇目录:

serdes芯片是干嘛用的

SERDES用在物理层与物理层通信,简单来说就是把低速并行信号转化为高速串行信号。

SERDES是序列化/解序列化器的简称,是一种实现高速、多协议通信的芯片设计技术,用于将并行数据转换为串行数据及将串行数据转换为并行数据。SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。

每个月。根据查询招聘软件得知,serdes高速接口设计薪酬为40000元每个月。SERDES接口作为高速串行通信的重要组成部分,对其芯片的研究和设计一直是一个热点。SOC是系统级芯片,ASIC是特殊应用集成电路。

电源噪声:SERDES需要提供稳定的电源和地线,以保证数据传输的可靠性。电源噪声会导致功耗增加。芯片面积:为了实现高速数据传输和支持多种数据接口标准,SERDES需要较大的芯片面积。芯片面积的增加会导致功耗增加。

据报道,Alphawave公司已经流片了业界首批使用台积电N3E制造技术(第二代3纳米级工艺节点)的芯片之一。

什么是SerDes

SERDES是序列化/解序列化器的简称,是一种实现高速、多协议通信的芯片设计技术,用于将并行数据转换为串行数据及将串行数据转换为并行数据。

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。ADC中文解释:模拟至数字转换器。serdes是串行器和解串器的简称,负责数据的合并。SERDES它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。

SerDes是Serialiazer和Deserializer的缩写,即串行化器/反串行化器。

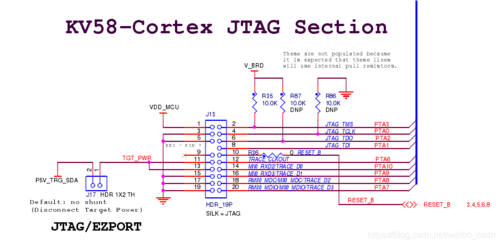

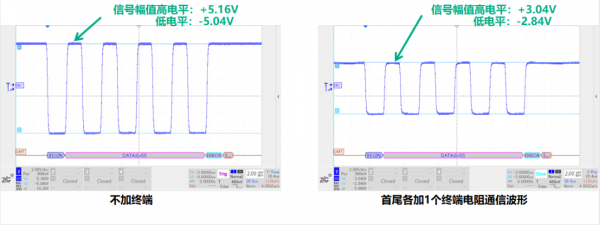

serdes是差分输出输入,各一对差分线。SGMII只是一个普通高速串行信号,SGMII--Serial Gigabit Media Independent Interface 。

FPGA的哪些和AD转换器连接?

1、一般在FPGA信号处理板中,为了提升信号的抗干扰能力,ADC和FPGA的连接以及FPGA和DAC的连接都使用的是差分接口 在FPGA内部进行信号处理时需要将差分输入转换为单端信号或者将单端信号转换为差分信号输出。

2、如果AD芯片是单输出,那么只需要将这个输出管脚与FPGA连接即可。另外,AD出来就是TTL电平信号,可以和FPGA直接连接。但要注意将FPGA的管脚配置为输入模式,还有要共地。

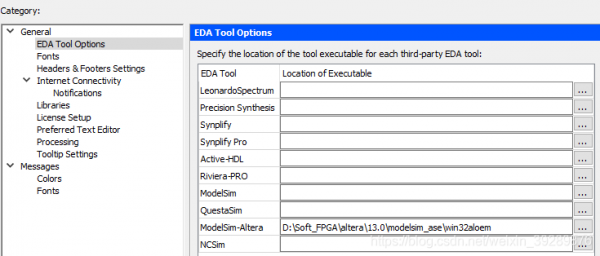

3、第二:就是ADC和FPGA的直接相连:Altera系列支持到支持600Mbps的器件有:cycloneIII,stratixII以上,还有最新的Arraia可以支持到LVDS 600+。Xilinx方面spartan3,vertix系列支持。第三:FPGA方面。

4、min VinL max等,看是否电平匹配。FPGA IO电平决定于对应BANK的VCCO的供电。如果电平不一致可以考虑将连接的BANK引入其他电平如5V。

5、关键在于AD转换后的信号的电气特性要符合FPGA要求,比如电压等等。

到此,以上就是小编对于spi电平标准的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏