本篇目录:

- 1、请用D触发器构成一个三位二进制减法计数器,写出实验原理。(可以画出电...

- 2、如何用D触发器实现2位2进制计数器电路图

- 3、74LS175的工作原理和电路图,使用时该怎么接

- 4、D触发器电路原理

请用D触发器构成一个三位二进制减法计数器,写出实验原理。(可以画出电...

个D触发器可以构成3位二进制计数器,计数范围0~7,因此其模为8。

设计一个3位二进制同步减法计数器(无效状态为001 100)计数器是用来统计脉冲个数的电路,是组成数字电路和计算机电路的基本时序部件,计数器按进制分可分为:二进制,十进制和N进制。

位二进制减法器 上图就是按上述规则接成的3位二进制减法计数器。图中采用上升动作的D触发器接成的T′触发器,其中所有D触发器的D= Qˉ即成为T′触发器。

如何用D触发器实现2位2进制计数器电路图

把N个带有反相输出端(D非)的D触发器串联起来,每个D触发器的反相输出端接到自己的D输入端,前一级的输出作为后级的时钟输入信号,就构成N位二进制异步计数器。

见下图:【补充】:异步计数器(亦称波纹计数器,行波计数器):组成异步计数器的触发器不是共用同一个时钟源,触发器的翻转不同时发生。分类:计数器按计数脉冲的输入方式可分为:同步计数器和异步计数器。

最佳答案 该设计主要思路为时钟分频和逻辑运算。也可以理解为计数器设计和进位提取。

选用芯片74LS74,管脚图如下。说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为 设计方案:用触发器组成计数器。触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数。

LS74是双D触发器,组两位异步加法计数器很简单,每个D触发器先构成一位计数器,然后Q0非输出端作D1的CP脉冲,逻辑图如下图所示。

【答案】:模8加/减计数器由三个D触发器计数单元经异步级联而成,在加法计数时,前级Q作下级时钟;减法计数时,前级Q作下级时钟。电路只需加入用X控制的异或门,即可在同一电路完成加/减计数的异步级联。

74LS175的工作原理和电路图,使用时该怎么接

ls175内部原理图:74ls175是常用的六D触发器集成电路,里面含有6组d触发器,可以用来构成寄存器,抢答器等功能部件。

ls175引脚图引脚图如图:74ls175内部原理图:74ls175是一种常用的六D触发器集成电路,包含六组D触发器,可以用来组成寄存器、应答器等功能元件。

单纯的告诉你什么功能,你没有什么长进的,你还是去画出它们的真值表吧。分别令那几个输入口为0或者1,有多少种组合就画多少组,然后根据真值表来看功能,很有用。

检修时.首先测得NE555③脚电位始终为低电平(正常情况下,该脚电位应每10秒钟左右电压跌落一次,持续约1秒钟左右).说明NE555未工作。

LS175就是d触发器 74LS20就是双4输入1输出的与非门(一片集成了两个门电路) 74LS00就是集成了4个与非门 至于抢答器的电路图 阎石版的数电第4版第4章课后习题的最后一道就有设计我给你拍下来就是了。

D触发器电路原理

1、触发器具有两个稳定状态,即“0”和“1”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。D触发器的次态取决于触发前D端的状态,即次态=D。因此,它具有置0、置1两种功能。

2、D触发器是一种通过检测电压变化来触发事件的电路。它包含一个电压比较器,一个延迟电路和一个触发电路。

3、在正向十六进制计数模式下,当 CLK 信号的下降沿到来时,第一个触发器的 D 输入端接入低电平,从而产生“0000”输出。

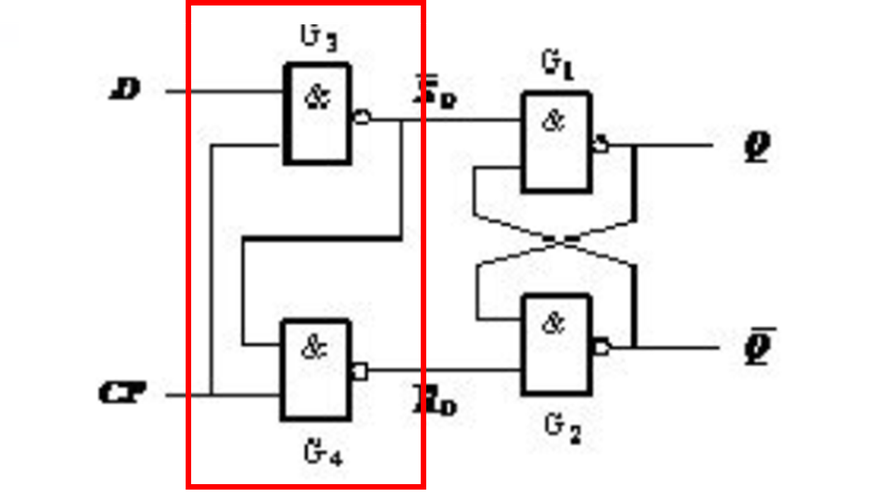

4、SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

到此,以上就是小编对于d触发器的功能是什么,如何实现的的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏