本篇目录:

- 1、ise文件分布图怎么看

- 2、怎样用modelsim做后仿真

- 3、FPGA自己手动布局布线是怎么操作的?

- 4、ise如何自动生成测试文件

- 5、如何使用ISE仿真器进行时序仿真

- 6、ise的coe文件怎么生成?

ise文件分布图怎么看

1、在设计流程中,可以在“sources”标签下的设计源文件中通过RTL代码手动创建状态转移图,也可以通过ISE工具中的流程编译器绘制状态转移图。同时,ISE可以将状态机转换成原始文件和编译器文件的形式,以便实现后端实现作。

2、ise的v文件在ise文件夹里,如果想打开需要通过插件,点击ise即可打开。

3、先check syntax(检查语法),通过后,没有问题就可以synthesize(综合),然后就可以看到rtl级的原理图,在左边processes的框框里面,点synthesize里面的VIEW RTL schematic。

4、在ISE中新建IP核,新建完成后找到存储该IP核的文件夹,在ipcore_dir文件夹下的几个文件中找下,该IP核的DATASHEET就在其中。

5、先点击右键,选择Full Screen,点击左键,就可以看到寄存器的波形。

6、打开ISE软件,打开原理图文件;点击“File”菜单,选择“Save As”;在弹出的对话框中,选择“VHDL Source”或“Verilog Source”格式,设置保存路径和文件名,点击“Save”即可将原理图保存为v文件。

怎样用modelsim做后仿真

1、iii. 我们将编辑过的脚本文件另存为sim.do, 在以后的仿真中我们可以在Modelsim命令行中,直接在脚本中运行do sim.do(当然是先需要将Modelsim的工作目录改到 工程所在文件夹/simulation/modelsim/)。

2、Simulation Model.。生成布局布线后仿真模型。切换到 Simulation ,选中Post-route。然后选test bench文件,双击下面的Simulate Post-Place&Route Model,启动modelsim。在modelsim中观察仿真波形。可以看到输出有明显的延时。

3、,ModelSim可以直接编译和添加Xilinx的库,目前的ise中(在开始菜单xilinx工具下找吧)直接有使用ModelSim编译库的工具。

4、打开ISE Project Navigator Edit-》Preference 在弹出的窗口中进行图示的设置 在XC6VLX240T上进行右击-》Design Properties 这个时候的仿真器选择Modelsim-SE verilog 便可以在ISE中调用modelsim进行仿真了。

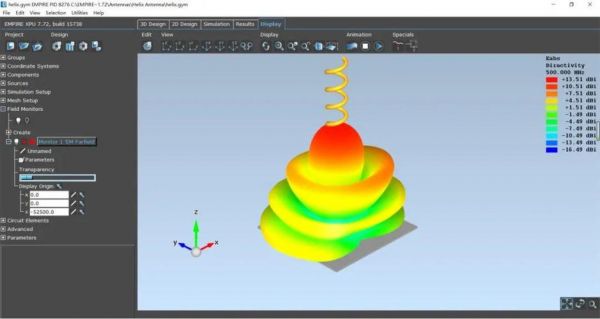

FPGA自己手动布局布线是怎么操作的?

确定需求:首先,需要确定FPGA芯片需要实现什么功能。这将有助于确定芯片的规格,包括芯片大小、输入/输出接口和逻辑资源数量等。选择开发工具:选择一种FPGA开发工具,例如Xilinx Vivado或Altera Quartus,以便开始设计。

时钟信号布线:FPGA和高速DAC的时钟信号必须保证正常传输和同步,因此需要避免布线过长,缩短信号路径长度;同时,在时钟信号传输过程中,需要注意信号阻抗匹配,以减少信号抖动和噪声干扰,提高信号稳定性。

进行布局布线:将逻辑电路映射到FPGA芯片的物理资源上,进行布局和布线,确定信号的传输路径和时序约束。 进行时序分析:对设计进行时序分析,确保信号的传输满足时序要求,避免出现时序冲突和时序违规。

ise如何自动生成测试文件

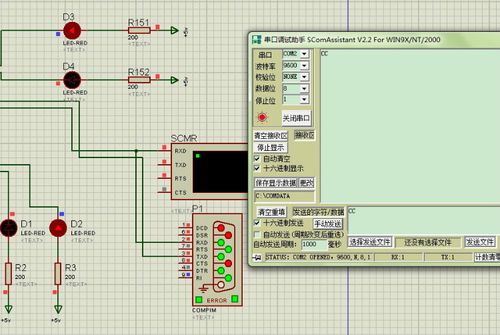

(1)在Source下,选择Post-Route Simulation。(2)将testbench文件添加进去。右键-Add Cope of Source...,选择testbench文件。(3)在Source下选择testbench文件,在Processes下,单击Xilinx ISE Simulator展开。

自带一个ROM_form.coe,经过编译器编译后会生成一个filename.coe,这是一个ROM格式的说明文件。

具体步骤如下:根据功能画出状态转换图 参考状态机写法,将你的图用verilog实现 按要求编写仿真平台testbench 状态机和测试平台编译通过后使用quartus或ISE调用modelsim仿真 仿真通过,设计完成。

打开XilinxISEDesignSuite软件,在ISE项目导航栏中,选择Sources选项卡,展开FPGA设计文件所在的工程文件夹。在工程文件夹中选择所需要查看的文件,右键单击该文件,选择Open-Schematic选项。

如何使用ISE仿真器进行时序仿真

ise15进行静态时序分析直接在设置里面选择静态时序分析点击开始。静态时序分析是一种通过检查所有可能的路径是否存在时序违规来验证设计时序性能的方法。

在文件树窗口‘sources’中找到FPGA芯片(例如‘xc3s500e-5pq208’)上点击右键,选择属性‘properties’。弹出project properties对话框。在对话框中将Simulator中选择,ISE Simulator (VHDL/Verilog)。关闭对话框就OK了。

可以用自带的仿真器,也可以调用modelsim,建议用modelsim。网上有调用的方法!希望能帮到你、。

如果是同步的模块的话,你在Testbench中,将生成CLOCK的代码修改,使之成为无限长的周期信号,然后仿真时会有一个默认的时间,也有一个默认的分辨率,将分辨率调大一些,这样在一个屏幕下显示的时长就会很长,不止1000ns了。

ise的coe文件怎么生成?

1、自带一个ROM_form.coe,经过编译器编译后会生成一个filename.coe,这是一个ROM格式的说明文件。

2、最后另存为,选择后缀为.coe,将文件导入到ROM以后,单击show,或者是显示初始数据的按钮(各个ISE不太一样),说明数据导入正确。对于ROM模块,主要是生成相应的.coe文件。

3、打开Guagle_wave软件,菜单栏,查看,全局参数设定,设定波形我们选择正弦波。用文本编辑器打开zhengxian.mif文件,将所需数据复制。在文档最前加入两行代码,用Ultraedit文本编辑器。

4、MIF文件是根据COE文件生成的。 COE文件只会在生成ROM模块时起作用,其作用就是根据文件内容生成相应的MIF文件,而ROM真正使用的是MIF文件。

到此,以上就是小编对于ise生成bit的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏