本篇目录:

- 1、vhdl哪个数据类型不必事先声明而可以直接引用

- 2、VHDL数据类型BIT、INTEGER和BOOLEAN分别定义在哪个库中?哪些库和程序包...

- 3、硬件描述语言vhdl的特点是什么

- 4、在VHDL中,七值逻辑各数据类型分别是什么含义?

- 5、在vhdl的ieee标准库中,预定义的标准逻辑位std-logic的数据类型中的数据...

vhdl哪个数据类型不必事先声明而可以直接引用

1、VHDL的程序包是放在设计库当中的,在引用程序包中的资源之前,首先用“LIBRARY”子句声明程序包所在的设计库:“LIBRARY 设计库名称;”,然后用“USE”子句声明所要引用的程序包:“USE 设计库名称.程序包名称.ALL;”。

2、这样就可以不用IEEE库中的std_logic_vector类型,而用自己声明的my_std_logic_vector类型了。

3、如果“不是只用函数的那个返回值,而是需要函数过程改变的那些量”的话,在VHDL中则不能描述成“函数”,而要描述成“过程”。

4、操作数可以是INTEGER,SIGNED,UNSIGNED或REAL数据类型,其中REAL类型是不可综合的。如果声明了ieee库中的包集std_logic_signed和std_logic_unsigned,即可对STD_LOGIC_VECTOR类型的数据进行加法和减法运算。

5、不一定有具体的硬件对应,因此往往在综合之后就不见了;而信号则具体指硬件中的信号线,即元件之间的连线,或者设计实体的端口连线,因此端口port必定是signal类型的对象。信号在综合之后一定会有硬件连线与之对应。

VHDL数据类型BIT、INTEGER和BOOLEAN分别定义在哪个库中?哪些库和程序包...

IEEE设计库:IEEE。设计库由若干程序包组成,每个程序包都有一个包声明和一个可选的包体声明。在设计库中,包声明和包体声明是分别编译的。

VHDL提供5个库,IEEE库,STD库,VITAL库,自定义库和WORK库 IEEE库包含的常用程序包有:std_logic_1164:常用数据类型(其中有std_logic、std_logic_vector数据类型)和函数的定义、各种类型转换 函数及逻辑运算。

数据库的常用数据类型如下:整数数据类型:整数数据类型是最常用的数据类型之一。浮点数据类型:浮点数据类型用于存储十进制小数。浮点数值的数据在SQLServer中采用上舍入(Roundup或称为只入不舍)方式进行存储。

基本数据类型有四类八种,分别为:整型:byte,short,int,long。浮点型:float,double。逻辑型:boolean。字符型:char。

这不是同不同的问题了,因为程序包包含于库中。比如,BIT数据类型的定义是包含在VHDL标准程序包STANDARD中的,而程序包STANDARD包含于VHDL标准库STD中。

number类型就是包括了所有的数字类型。可以是integer也可以是numericOracle数据类型之numberoracle的number类型是oracle的内置类型之一,是oracle的最基础数值数据类型。

硬件描述语言vhdl的特点是什么

1、在行为级抽象建模的覆盖范围方面软语言比VHDL略差一些。FPGA的硬件描述语言VHDL,超高速集成电路硬件描述语言,符合美国电气和电子工程师协会标准,利用一种和数字电路基本知识结合较密切的语言来描述数字电路和设计数字电路系统。

2、VHDL用来描述硬件。硬件系统中的所有部件都是同时工作的,所以VHDL结构体中的语句都是并行语句,与书写顺序无关。每一个并行语句都描述了一个电路部件,这些部件同时工作。

3、(1)与其他硬件描述语言相比,VHDL具有以下特点:(2)功能强大、设计灵活。(3)强大的系统硬件描述能力。(4)易于共享和复用。

4、软件编程语言是顺序执行的,而硬件描述语言(比如vhdl)描述的硬件却是并行工作的,所以硬件描述语言中的语句是并行语句,没有先后顺序问题。

在VHDL中,七值逻辑各数据类型分别是什么含义?

这不是一两句就能说明白的。你需要有数字电路的基础知识,例如CMOS反相器、TTL反相器、线与、三态门、上拉电阻、下拉电阻等概念。如果你已经具备这些知识,则比较容易弄懂七值逻辑,否则会是一头雾水。

就是最终可以用FPGA内部寄存器的逻辑来实现比如,加法、减法、乘法、赋值什么的都是可综合的,但是如,文件读写等仅能在仿真中使用,不可能烧写到FPGA中去。所谓综合,就是将设计向前推进的过程。

整型(int)表示整数类型,包括正整数、负整数和零。浮点型(float/double)表示带有小数部分的数值类型,其中float表示单精度浮点数,double表示双精度浮点数。

【答案】:数据对象(常量、信号、变量)是数据的载体,常量通常被实现为编程器件中的固定电平,变量通常被实现为暂存单元,信号和变量通常被实现为连接线。

在vhdl的ieee标准库中,预定义的标准逻辑位std-logic的数据类型中的数据...

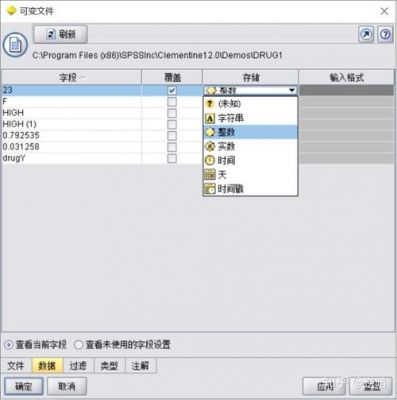

1、std-logic是一种枚举类型的决断子类型。这种枚举类型有9个值:U,X,1,0,Z,W,H,L,-,所谓数据,就是指std_logic类型对象(信号、变量或者常量)的值,可以是上述9个值当中的某一个。

2、use ieee.std_logic_arith.all;-- entity fenx is --实体说明,fenx 实体名 port --端口 (clk:in std_logic;--clk为端口名,in 为端口类型,这里是输入,std_logic指的是标准逻辑数据类型。

3、将把STD_LOGIC_VECTOR转换成有符号数进行运算。与std_logic_vector的定义完全相同。所不同的是表示的意义不同。举例来说:一定要重视signed与unsigned这两种类型。shift_left() and shift_right()具体用法在此不赘述。

4、std_logic是在IEEE的std_logic_1164程序包中说明的一种类型,其值的设定可以与std_u logic相同。

5、而在利用标准逻辑型对端口或信号进行说明以前,在整个程序的最开始,必须有如下调用语句。LIBRARY IEEE;USE IEEE.STD_LOGIC_116ALL;STD_LOGIC_1164程序包,其中预定义内容为STD_LOGIC,STD_LOGIC_VECTOR等数据类型。

到此,以上就是小编对于vhdl的三种数据对象中文分别是的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏