本篇目录:

- 1、allegro16.3,怎么防止重叠元件而不显示DRC

- 2、allegro16.3做DRC没有报错

- 3、EstudioPro-PCB转原理图

- 4、如何修改Allegro中的DRC错误

- 5、【Candence使用笔记】allegro过孔在焊盘上怎么不显示DRC

allegro16.3,怎么防止重叠元件而不显示DRC

1、是的,就是和place bound 有关的。但是这个DRC可以关掉的,“setup”--“constrains”--“modes”--“design modes(package)”,在“package to package”后面选择“off”。

2、方法一:Setup--Constraits--Mode--SMD Pin Modes--via at smd fit required--off 不推荐此方法的原因是:该操作会同时关闭PCB图上所有此类DRC错误,可能会隐藏掉非主动放置在焊盘上的过孔错误。

3、正常来说,PLACE_BOUND_TOP这层只在布局的时候使用到,两个元件的PLACE_BOUND_TOP有重叠时,系统会报DRC错误。并且PLACE_BOUND_TOP的大小应该是封装的实际大小的,所以布局时,一般去掉此项的显示,只看silkscreen_top层。

4、在PCB Editor中,Setup→Constraints→Constraint Manager,针对你的DRC错误,在左侧选择DRC类型,然后再根据需要在右侧修改相应的蓝色字体即可。

5、芯片引脚间提示DRC错误,这两个引脚是不是不同的网络属性,如果你在规则设置中定义了这两种网络的线宽、线距、或者线至焊盘间距、焊盘间距,肯定是这些值定义的过大而产生的错误,芯片引脚本身肯定是没错的。

allegro16.3做DRC没有报错

1、是的,就是和place bound 有关的。但是这个DRC可以关掉的,“setup”--“constrains”--“modes”--“design modes(package)”,在“package to package”后面选择“off”。

2、首先,你这个PIN应该没有加ViaKeepout这一层,所以没有K/V的错误。关于同名DRC,从图上上面一个DRC可以知道,因为你VIA小于一半在PIN上,就会报,如果VIA有超过一半在PIN上,这个DRC就不报,证明是正常连接的。

3、如果有DRC错误,就在PCB会出现红色的警告的,比如“PP”,这个是package和package之间的间距小于规则设置。可以在网上搜索所有的DRC错误,就能判断哪块有问题了。

4、Rules Options中点击“确定”按钮,提示框点击“是”按钮;DRC错误全部显示在屏幕下方的对话框中,也可以双击xx.drc查看DRC报告。注:xx为项目名称。在Physical Rules中可以设置是否检查有无PCB封装和封装是否无效。

5、方法一:Setup--Constraits--Mode--SMD Pin Modes--via at smd fit required--off 不推荐此方法的原因是:该操作会同时关闭PCB图上所有此类DRC错误,可能会隐藏掉非主动放置在焊盘上的过孔错误。

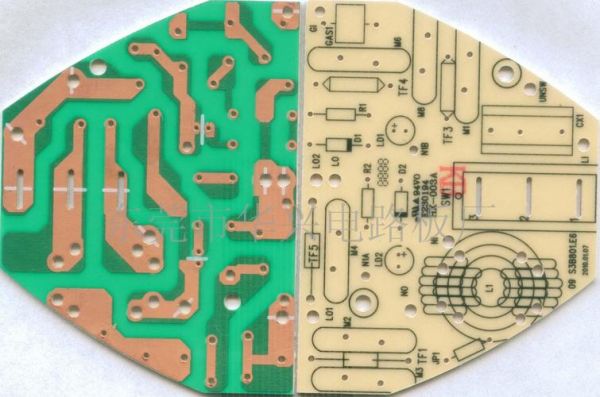

EstudioPro-PCB转原理图

1、先将pcb文件的网络表导出来。用Omninet for Windows,E-Studio等软件将其转换0rcad格式的文件。再将orcad格式的文件用protel打开即可。

2、PCB图转成SCH原理图,需要进行手工作图,按照PCB元件编号,确定好每一个元件后,手工画线,画好后,从PCB更新SCH原理图,要求无报错。

3、浪费时间。如果实在要用就自己画,或者找别人做反向工作的。我是夜猫PCB工作室的 。做了N多年PCB设计工作了。没听过这个能转。 。

4、点击“Design”中的子菜单“Update PCB Document XXXXXX.PcbDoc”根据习惯,在弹出的对话框中,选择去掉”Add Rooms“项(完全是习惯问题,可以不去)点击”Execute Changes“按钮执行更新 等待执行完毕。

5、新建 Workspace 通过菜单 File Save Design Workspace 保存工作空间,我们命名为:zhihu.DsnWrk。

6、在计算机上打开AltiumDesigner软件,创建一个新的项目文件,然后创建一个新的原理图文件。创建一个新的PCB文件后保存所有文件,确保成功保存所有文件。

如何修改Allegro中的DRC错误

1、芯片引脚间提示DRC错误,这两个引脚是不是不同的网络属性,如果你在规则设置中定义了这两种网络的线宽、线距、或者线至焊盘间距、焊盘间距,肯定是这些值定义的过大而产生的错误,芯片引脚本身肯定是没错的。

2、是的,就是和place bound 有关的。但是这个DRC可以关掉的,“setup”--“constrains”--“modes”--“design modes(package)”,在“package to package”后面选择“off”。

3、方法一:Setup--Constraits--Mode--SMD Pin Modes--via at smd fit required--off 不推荐此方法的原因是:该操作会同时关闭PCB图上所有此类DRC错误,可能会隐藏掉非主动放置在焊盘上的过孔错误。

4、根据提示来改呗,哪里有问题改哪里,一般错误那里有红色的英文字母代号,比如P指的是焊盘,L指的是走线。

【Candence使用笔记】allegro过孔在焊盘上怎么不显示DRC

可以直接在热焊盘上面打VIA,如下图所示~可以用复制的方法,如果需要slide,可以把右边的allow DRC勾选上即可移动了。

方法一:把PIN关掉,再在相应区域打孔,孔就不会乱跑了,但是看不见焊盘轮廓打的孔位置不够好,因此打完后再把PIN打开、再用slide命令调整。

设置想要显示的单位,mm或者mil Find中勾选Cline segs,点击感叹号,双击走线,查看结果。

PCB layout时候不能删除,出gerber的时候不出内层无网络的焊盘就可以,gerber选项里有这一项勾选。

了解和掌握这款最新的优秀EDA软件用法。 七 电子线路的设计过程 EDA就是“Electronic Design Automation”的缩写技术已经在电子设计领域得到广泛应用。发达国家目前已经基本上不存在电子产品的手工设计。

到此,以上就是小编对于allegro怎么检查差分有没有pn等长的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏