本篇目录:

- 1、vivado生成bit文件如何选flash型号

- 2、Vivado安装、生成bit文件及烧录FPGA的简要流程

- 3、VIVADO中MSB怎么设置

- 4、verilog的tb文件怎么写

- 5、Modelsim的自动化使用(一)脚本的基本使用

vivado生成bit文件如何选flash型号

生成bit文件。使用bit文件生成mcs文件,生成的mcs文件时的flash参数要与实际使用的flash参数一致。JTAG线连到板子上,打开hardware manager,识别出器件。鼠标点击扫描出的器件,右键点击器件,选择add configuration memory device。

打开后选择左边的loadlicense选项卡:点击copylicense,选中刚才安装目录中的crack文件夹中的license.lic:至此Windows下的XilinxVivadoDesignSuite已经全部安装完成。

默认设置,next,点击OK,选择dowmload.bit打开,选择NO,不再添加器件,点击OK,双击左侧ganerate file,生成Prom的下载文件mcs文件,mcs文件成功生成,关闭软件,重复1,2,3步操作,出现下图。

第一种bit文件是烧进板子,板子下电即擦除,可以烧其他bit文件覆盖,速度一般较快 第三种bin文件是烧进板子中的flash(如果你板子中有flash),下电也不会被擦除,下次上电直接用,就不用再烧了。

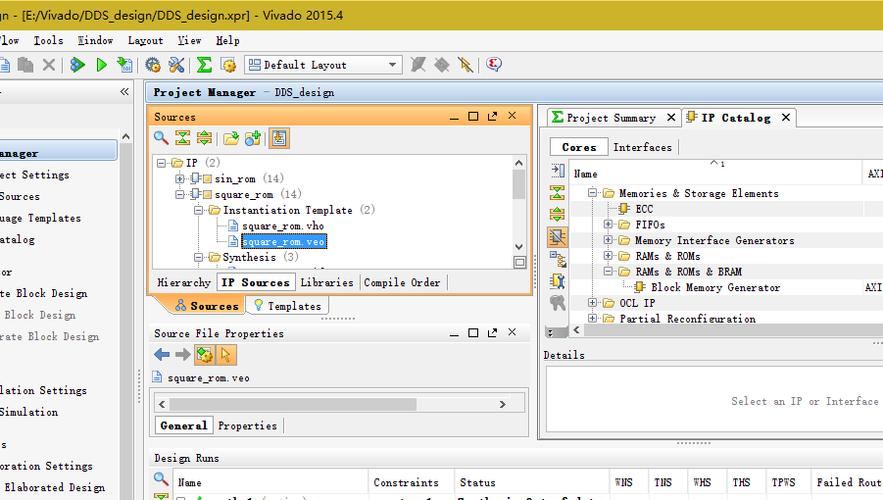

下载好bit文件后的界面如下图所示。 这里有个问题,Vivado 2012中,Debug Probes窗口不会自动打开,可以再Windows选项单中找到该窗口。 打开Debug Probes窗口后的界面如下图所示。

如果是裸机的程序,那么可以用jtag转接板连接到电脑上,用ads来调试和仿真。如果是boot loader一般也是jtag转接板连到电脑,通过H-JTAG烧写nor flash或者nand flash,把boot loader烧进去。

Vivado安装、生成bit文件及烧录FPGA的简要流程

1、首先下载vivado webpack installer,目前最新版本为2011。开始安装,可以选择VIvado HL Webpack版本点击next继续安装。接下来的一步可以使用默认选项继续安装,但是这样占用的存储空间比较大。也可以使用如用所示的最小安装方式。

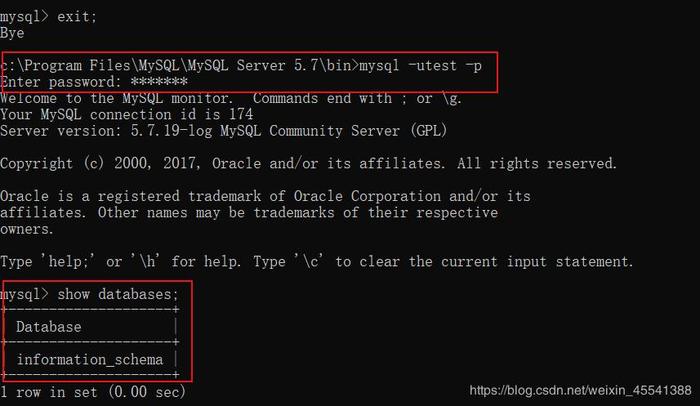

2、首先要去下载vivado的安装包。建议去官网下载下载好了安装解压。这个时间有点长。安装好了就打开,打开之后会出现三个问题,三个全选I Agree,然后点击NEXT。

3、以下是FPGA开发的基本流程:需求分析和规划 在开始FPGA开发之前,首先需要明确应用场景和需求,例如数据加速、信号处理、图像处理等。根据需求,进行系统架构规划和算法设计。

4、将代码烧录到到 flash 步骤 1)点击 bitstream setting ,将 bin_file 勾上,点击 OK。2)点击 generate bitstream ,生成 bit 文件和 bin 文件 3)点击 open hardware manager,连接板子。4)选中芯片,右键如下操作。

5、确定需求:首先,需要确定FPGA芯片需要实现什么功能。这将有助于确定芯片的规格,包括芯片大小、输入/输出接口和逻辑资源数量等。选择开发工具:选择一种FPGA开发工具,例如Xilinx Vivado或Altera Quartus,以便开始设计。

6、再下一步,这样ILA的设置工作就完成了。可以在debug视图中看到,Vivado自动帮我们插入了dbg_bug和ila,接下来生成bit文件,写入FPGA中,在Vivado的调试界面上就能进行在线的波形输出了。

VIVADO中MSB怎么设置

选择vivado菜单“Tools”——“Compile Simulation Libraries...”命令。

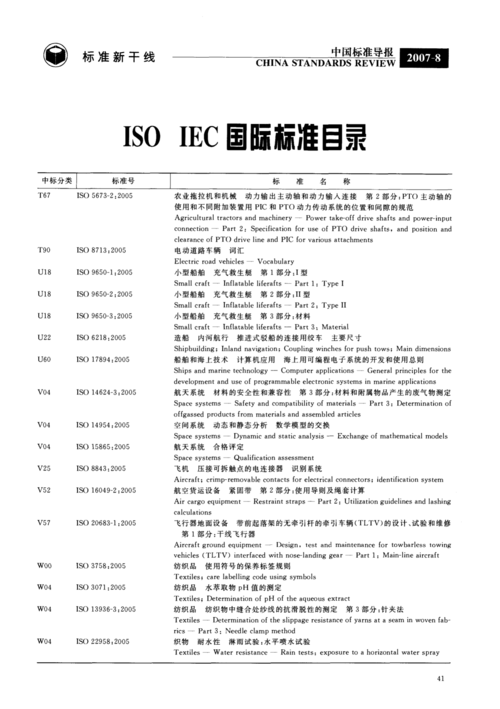

设置spi的宽度是 open implement 在菜单tool下面有个属性设置里有类似原来是impact转换工具。vivado基本知识:Vivado设计套件,是FPGA厂商赛灵思公司2012年发布的集成设计环境。

你可以在ISE工程中导入HLS生成的源代码。 一般一个季度出一个新版本。建议在Xilinx主页下载一个Document Navigator,将Vivado的User Guide阅读一下。有问题时再到相应文档中搜索相关的使用办法。

step编辑源码,保证其编译通过 step修改bsp的mss、mld、tcl文件 step制作模板工程,将模板和BSP文件夹一起放到自己喜欢的路径下 step在SDK中设定repository的路径 step创建工程并测试。

verilog的tb文件怎么写

要测试这段代码,你需要准备一个测试文件。测试文件中需要定义输入信号、输出信号和测试用例。

tb在verilog的全称是testbench。对于简单的module来说,要在modelsim的仿真窗口里面看波形,就用addwave..命令。比如,testbench的顶层module名叫tb,要看时钟信号,就用addwavetb.clk。

方法如下:verilog中数据的写入分为三步: $fopen()打开文件。、$fwrite()写入相应data 。、$fclose()关闭文件。

Modelsim的自动化使用(一)脚本的基本使用

打开任务计划程序:在 Windows 中,按下 `Win + S` 组合键来打开搜索功能,然后输入“任务计划程序”或“任务计划”,然后选择打开。创建基本任务:在任务计划程序中,选择“创建基本任务”选项。

自动化测试脚本的基本功能有脚本语言,对象识别,自动执行和结果判断。测试需求分析阶段。测试需求分析阶段主要工作是获得测试项目的测试需求(测试规格)。输出产物:《可测试性需求说明书》和《测试规格》。

其次,运行第一个matlab脚本文件,使用cd命令切换到下一个文件夹。然后,运行下一个matlab脚本文件,通过编写一个包含以上步骤的函数或脚本,自动化过程。

设定仿真工具 assignmentsettingEDA tool settingsimulation 选择你需要的工具。

了解自动脚本精灵:自动脚本精灵是一种自动化工具,可以记录和执行一系列预定的操作步骤。可以使用自动脚本精灵来模拟键盘和鼠标操作,从而执行一系列烧烤摊的管理任务。

到此,以上就是小编对于vi文件怎么保存的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏