本篇目录:

- 1、如何在VIVADO中编译仿真库

- 2、vivado怎么创建DATA文件夹

- 3、vivado怎么生成模块连线图

- 4、怎么把将coe文件加载到blockrom所生成的rom中

- 5、怎么实现同一测量点输出方波,正弦波,三角波

- 6、怎么用vivado生成bin或者mcs文件?

如何在VIVADO中编译仿真库

1、安装了vivado2014,使用vivado生成了一个FIFO。在vivado中编译仿真库后发现不像之前一样有Xilinxcorelib这个库了。也就没有IP对应的仿真库了。

2、step编辑源码,保证其编译通过 step修改bsp的mss、mld、tcl文件 step制作模板工程,将模板和BSP文件夹一起放到自己喜欢的路径下 step在SDK中设定repository的路径 step创建工程并测试。

3、只包括了自己实际验证的部分。ug94ug897都是很好的学习Vivado System Generator的资料,讲的非常详细,英文也不难,所以这里不打算像之前一样一步步的写下来了,有了前面的基础和一点matlab的基础应该可以很快上手的。

4、在Settings里勾选-bin_file选项,如图1所示。添加约束文件到工程中,如图2所示。编译项目即可生成.bin文件。选择ToolsGenerate Memory Configuration Files...,如图3所示。

vivado怎么创建DATA文件夹

1、特别需要指出的是 Flow Navigator只有在Vivado IDE中打开 .xpr 工程文件才会显示,如果打开的是设计检查点 .dcp 文件(不论是工程模式或是非工程模式产生的dcp)都不会显示这个侧栏。

2、解压缩之后会得到文件夹,如何启动Vivado呢?touch a.sh 创建一个.sh文件 对这个文件进行编辑,vi a.sh,将上述命令写入该文件中。在命令行下面进入到sh文件的目录,执行chmod +x a.sh,在执行./a.sh。

3、(1)把想要观测的信号线加入在线逻辑分析仪中。(2)上板测试,trigger到想要的实时数据,用一句TCL语句保存为ila格式的文件,那句话是write_hw_ila_data data1 [upload_hw_ila_data hw_ila_1] 。

4、vivado的安装源码在ZEDBOARD-SYNQ开发板的附带光盘中有,如果无光盘可以前往http://下载。

5、我想修改工程中RAM中数据,而不需要重新综合、布局布线,看到在ISE中有Data2MEM功能,但也不知道具体怎么用。

vivado怎么生成模块连线图

Vivado Logic Analyzer的使用 chipscope中,通常有两种方法设置需要捕获的信号。

如下图所示,运行增量流程的前提是有一个已经完成布局布线的.dcp文件,并以此用来作为新的布局布线的参考。运行过程中,Vivado会重新利用已有的布局布线数据来缩短运行时间,并生成可预测的结果。

vivado设计时要专门设计ad模块。官方例程路径AD-FMCDAQ2-EBZ开发板资源主页在页面下方下载全部的资源库,后续根据指引自己make生成工程文件,下载并解压资源文件,接下来按照官方的指引一步步生成工程文件。

再下一步,这样ILA的设置工作就完成了。可以在debug视图中看到,Vivado自动帮我们插入了dbg_bug和ila,接下来生成bit文件,写入FPGA中,在Vivado的调试界面上就能进行在线的波形输出了。

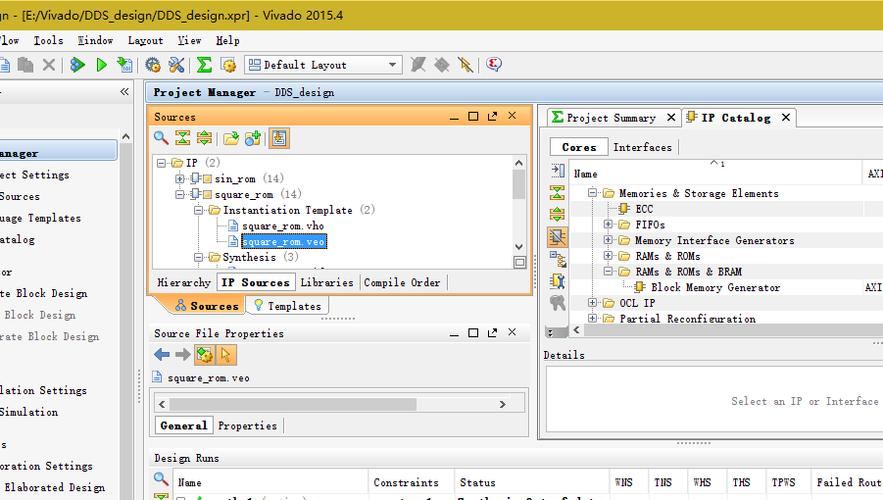

设计DDS的核心就是调用IP ROM,vivado调用ROM的方法和ISE相类似,都是加载.coe文件,我这里特地做笔记,以防忘记。

怎么把将coe文件加载到blockrom所生成的rom中

always enable是ROM一直处于工作状态,不需要使能信号。这里是加载.coe文件,勾选load init file 然后点击browse将刚才生成的square.coe文件加载到ROM中,最后点击OK。

第一步 生成波形数据 可以使用mif精灵,或者matlab生成一个coe文件,文件内容格式具体如下图:第二步 定义ROM IP核 定义一个但端口的ROM IP核,一个波形深度为1024,则存放四个波形的深度需要4096,对应的地址位为12位。

在matlab中将数据录入,如果数据是在txt文件中,可以读文件录入(网上很容易找到相关命令)。将数据存成n行1列的数组。通常录入的数据都是10进制的。

可能的原因是你在生成时并没有+.coe文件,结果默认生成一个空白的ROM。而在modelsim里面你又把.mif文件添加到库中。所以会出现告警。解决方法:重新生成一个~~~在initial content 下面选择load file。

),并在最后一行添加一个分号逗;地。最后,在文件的最开始添加下面两行:memory_initialization_radix=10;memory_initialization_vector= 然后,保存文件退出。将coe文件加载到BLOCKROM所生成的ROM中。

怎么实现同一测量点输出方波,正弦波,三角波

1、方案3见图3,特点是也先产生方波,而后通过积分器或其它电路产生三角波,再用有源滤波器产生正弦波;最后通过幅值控制和功率放大电路输出信号。

2、采用单片机定时器实现 采用运算放大器和RC阻容电路实现 三角波产生方案:主要方法是采用方波加积分器实现。此外,上述三种信号均可采用DDS或信号发生器专用芯片实现。

3、波形和频率的改变通过软件控制,幅度的改变通过硬件实现。 正弦波是频率成分最为单一的一种信号,因这种信号的波形是数学上的正弦曲线而得名。任何复杂信号——例如音乐信号,都可以看成由许许多多频率不同、大小不等的正弦波复合而成。

4、一种方法使用max038来产生正弦波,方波,三角波,支持输出频率为0.1Hz-20MHz。这种方式外围电路比较简单,一般只要电路图正确就可以正常工作。

5、建议采用多波形发生器专用集成电路ICL8038,它可以同时输出你要的各种波形。该IC可以双电源工作。并且调频方便。电路见图。

6、一片 8038,能同时输出:方波,正弦波,三角波。

怎么用vivado生成bin或者mcs文件?

在Settings里勾选-bin_file选项,如图1所示。添加约束文件到工程中,如图2所示。编译项目即可生成.bin文件。选择ToolsGenerate Memory Configuration Files...,如图3所示。

第一种bit文件是烧进板子,板子下电即擦除,可以烧其他bit文件覆盖,速度一般较快 第三种bin文件是烧进板子中的flash(如果你板子中有flash),下电也不会被擦除,下次上电直接用,就不用再烧了。

使用Vivado制作FPGA的简要流程在Windows下安装XilinxVivadoDesignSuite:XilinxVivadoDesignSuite安装文件,解压后得到安装目录:运行xsetup.exe文件,进入安装程序。如果提示要更新就直接点continue关掉。

生成bit文件。使用bit文件生成mcs文件,生成的mcs文件时的flash参数要与实际使用的flash参数一致。JTAG线连到板子上,打开hardware manager,识别出器件。鼠标点击扫描出的器件,右键点击器件,选择add configuration memory device。

确认bit文件的电流设置:- 检查生成MCS文件使用的原始bit文件的设定。- 使用相应的软件或工具来查看bit文件中的电流设置并进行确认。 检查电流配置文件:- 确认所使用的编程器或烧录器是否需要额外的电流配置文件。

到此,以上就是小编对于vivado详细使用教程的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏