本篇目录:

怎么用74HC194设计一个101011的序列检测器,可重叠

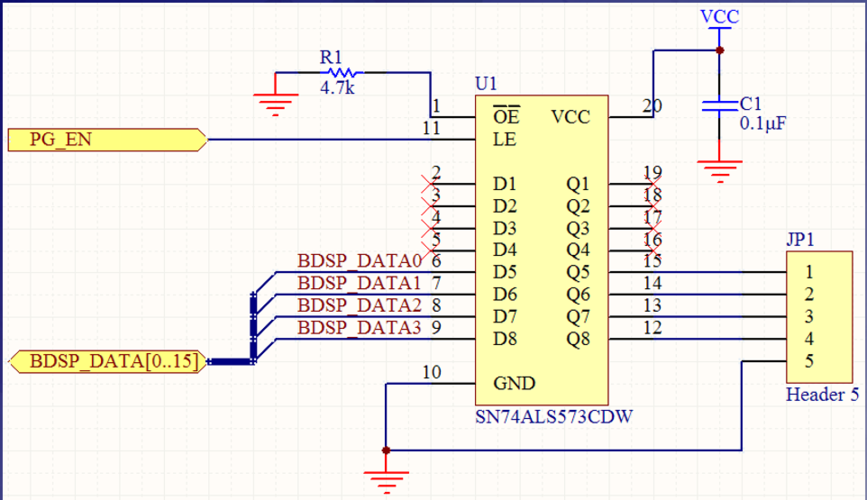

1、设194输出为ABCD,则需要满足A/BCD=1,A、C、D接与门输入,/B接非门后再接与门输入。与门输出只有在A/BCD=1011时输出高电平,点亮发光二极管。

2、在电脑的dos命令界面中输入 mysql --version,来获取mysql的版本号,注意version的两个横线和之前的mysql是有一个空格的。获取了我们的mysql版本号,就开始建立触发器了。

序列信号检测器不可重叠检测应怎样设计

1、(2)掌声速度应与电路的时钟一致(例如1次/秒),电路中设一个LED指示时钟脉冲变化。(3)若输入一次开锁信号未将锁打开,可重复三次,否则,启动音响报警电路并自锁。发挥部分:(1)当锁打开时有机械执行机构动作。

2、这里可以不用串并转换,逐次将isignal[7:3], isignal[6:2], isignal[5:1], isignal[4:0]和10101对比即可实现。

3、操作步骤:检查器材,检查实验所需器材是否齐全;组装一个电路检测器。

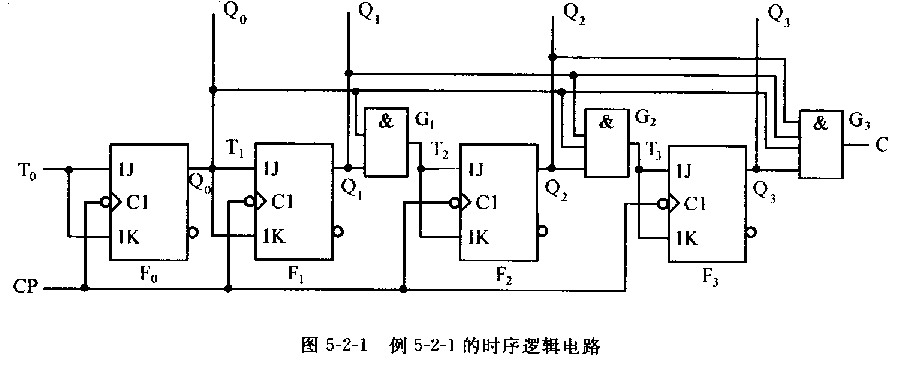

4、.写出设计过程,并记录实验结果。设计过程用JK触发器设计一个8421码十进制同步加法计数器。(1).状态真值表:(2)激励方程:,(3)电路图:2.用D或JK触发器设计一个110串行序列信号检测器。

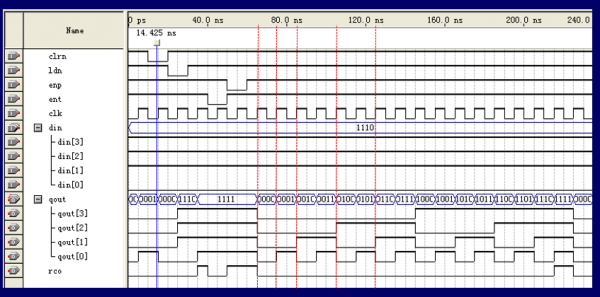

5、然后检测到了1100的序列就输出 最简单的方法就是用四个flipflops, 这样你就有了最近四个周期的输入序列的数值,然后当这四个值是1100的时候输出1就好。 还有一个方法是状态机。如下图。

6、在电脑的dos命令界面中输入 mysql --version,来获取mysql的版本号,注意version的两个横线和之前的mysql是有一个空格的。获取了我们的mysql版本号,就开始建立触发器了。

序列检测器输入怎么接

1、序列检测器:将一个指定的序列从数字码流中识别出来。

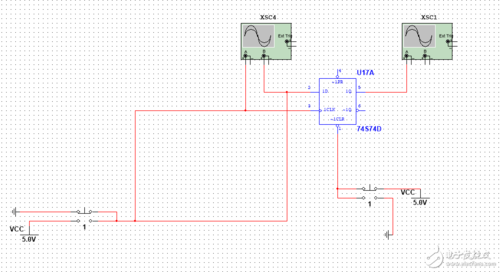

2、序列发生器——用4个D触发器串联,接同步时钟信号,形成同步移位寄存器,每个触发器的输出端都引出来,人工输入1011来使1011序列出现。

3、每次并行检测2位,比如判断x输入两位是否等于10,后两位等于10,再两位等于11,最后两位等于01?如果是这样,可以将x串行输入,进行个串并转换,例如用一个寄存器reg1[1:0]保存其值。

4、这是以前用VHDL语言写的一个数字序列检测器,当检测到“1101”时,则y输出一个高电平。根据你的情况,可以把四位检测位改到八位,道理一样。可以把输出Y接到LED1的正端。在仿真时,CLK设置为1KHZ就可以了。

5、序列检测器是时序数字电路中非常常见的设计之一。它的主要功能是:将一个指定的序列从数字码流中识别出来。在接收端对收到的受干扰的信号时利用信号概率和噪声功率等信息按照一定的准则判定信号的存在,称为信号检测。

到此,以上就是小编对于序列检测器设计思路的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏