本篇目录:

- 1、求助一个关于xilinx的FPGA加载问题

- 2、如何将程序加载到FPGA

- 3、FPGA高手请进来:问一个xilinx的FPGA问题

- 4、FPGA上电不能自动加载PROM里面的程序

- 5、如何实现远程FPGA版本更新和重启

- 6、FPGA动态重加载lut跳过bram过程

求助一个关于xilinx的FPGA加载问题

再仔细查下硬件,尤其是电阻的问题上,是不是有某个地方接了不该接的电阻了。

比较简单的方案:使用xfc08p这种配置芯片。它可以通过REV_SEL_0和1选择FPGA需要加载的程序版本,最多4个。主动FPGA可以通过这两根线控制从FPGA加载的版本,然后控制从FPGA的PROG_B(低脉冲有效)启动加载过程。

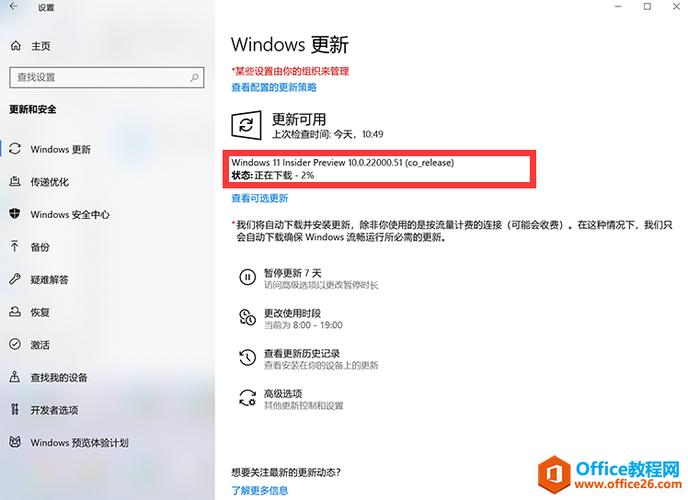

就是因为他本身系统不支持,我觉得你可以再试上一段时间,因为这个东西我觉得还是要重新去卸载,这样可能会比较好。

用万用表测试管脚,检查线路物理连接情况是否良好。下载代码时,更换接入管脚重试,看是否是某个管脚断裂导致没写进去 在1和2没问题的前提下,只能更换FPGA芯片。

顶层名称与edf网表名称不匹配、Verilog代码的规范性问题、底层Xilinx编译器错误等原因。顶层名称与edf网表名称不匹配:LabVIEWFPGA需要确保顶层名称与edf网表名称相匹配,否则会导致编译错误。

如何将程序加载到FPGA

1、上传文件运行。根据查询IT之家官网显示。首先将FPGA程序文件上传到terminal设备。其次确认已连接到FPGA设备串行终端。接着在终端中输入命令加载和运行FPGA程序。最后等待terminal加载完成,即可运行。

2、连接到FPGA板子:首先需要将计算机与FPGA板子连接起来,并确保能够正常通信。 打开终端窗口:打开终端窗口,并输入相应命令以进入U-Boot引导程序界面。

3、如果你的microblaze的程序小,可以放在FPGA内部的例化ROM中,然后生成的BIN文件可以作为ROM的初始化文件导入,这样可以与FPGA加载文件一起存。否则只能你自己敲代码去实现这部分功能。

4、如果是下载到FPGA芯片中的话,就直接生成电路了,程序就已经开始运行了。如果是烧写到了flash中的话,就需要断电,重新上电,fpga从flash重新加载生成fpga中的电路。

5、当然,如果这些小项目全部都是分立的话,也可以直接用线将他们连接起来,也就是 Element mapping。

6、首先CPLD资源一般是都不够的。如果你要用CPLD先接收配置文件,然后再配置FPGA,你肯定要用到CPLD里的BlockRam。现在Altera的MAX系列都没有BlockRam,Lattice的MACHXO最大有512K的BlockRam,肯定不够。

FPGA高手请进来:问一个xilinx的FPGA问题

1、比较简单的方案:使用xfc08p这种配置芯片。它可以通过REV_SEL_0和1选择FPGA需要加载的程序版本,最多4个。主动FPGA可以通过这两根线控制从FPGA加载的版本,然后控制从FPGA的PROG_B(低脉冲有效)启动加载过程。

2、逻辑块:Xilinx FPGA提供了多种逻辑块,如查找表(LUT)、寄存器文件(Register File)、算术逻辑单元(ALU)、多路复用器、时钟管理器等。这些逻辑块可以根据您的设计需求进行选择和组合。

3、内核时钟网络:这是FPGA内部的核心时钟网络,用于驱动FPGA的各种内部功能模块。内核时钟网络通常由多个时钟源产生时钟信号,并通过复杂的时钟树映射到FPGA的各个部分。 时钟树:这是连接内核时钟网络和FPGA外部接口的桥梁。

4、如果你的项目不是太大,没必要用Synpoify,用ISE自带的综合工具就行了。如果你不设定时钟,综合工具会自动为你选定的,因为全局时钟资源的信号传输很好,不用就浪费了。

5、XILINX的Block RAM每块是16K bit,可以配置成16K X1,8K X2,4KX4,。。一直到512X36。你要实现的是124000X5 bit,当然不管内置的还是外置的RAM,都没有5 bit的宽度,一般还是要到8位的。

FPGA上电不能自动加载PROM里面的程序

1、在impact里面JTAG链里面你应该能看到一个PROM,右键加载生成的这个二进制文件,下载进去,下次板子上电,PROM里面的程序就会自动被FPGA读取。

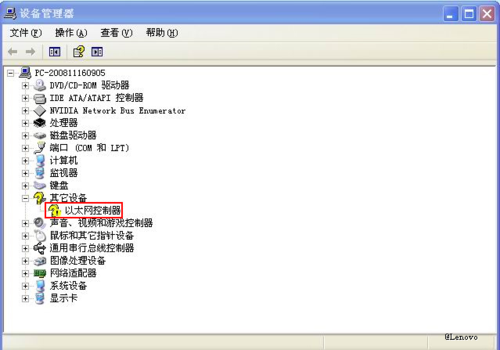

2、FPGA芯片未正确上电或是芯片已经烧毁。建议先检查电源是否正常,是否正常供电,其次检查芯片及下载器。

3、在加载时需要在这种情况下,我可以使用单个Config PROM将我的位文件加载到FPGA,如果是正确读取PROM,应该选择连接FPGA和PROM,以便相应的配置加载到两个FPGA中。

4、ROM是只读。不是每一次上电才加载程序。它本身就能存储。

如何实现远程FPGA版本更新和重启

当FPGA启动时,加载控制器会从地址0开始读取加载指令。当读到WBSTAR和IPROG指令时,控制器就跳转到WBSTAR指定的地址读取新的加载指令。在第二个配置文件中不再发IPROG指令,控制其将顺序执行以直到配置文件结束。

用CMD环境命令shutdown实现: 例:shutdown /s /p /f /m \\171100 /user:administrator password 即可。

方法三:硬件远程重启服务器 当然如果此时服务器卡住不能联网,那么用一般的远程桌面连接方式就不能实现。推荐可以使用网络人电脑远程开机卡。远程开机卡是一款通过拨打电话实现唤醒远程电脑的启动设备。

具体操作是在命令提示窗口中执行“shutdown /m \\服务器IP地址 /r”,这样服务器将自动重新启动。我们在ping -t命令窗口中也将看到目的网络连接情况从畅通到requeset timed out,这说明目的服务器已经在进行重启操作。

FPGA动态重加载lut跳过bram过程

具体如下:内部配置访问端口(ICAP)是基于XilinxSRAM的现场可编程门阵列(FPGA)中实现的任何动态部分可重配置系统的核心组件。我们开发了一种新的高速ICAP控制器,名为ACICAP,完全采用硬件实现。

资源消耗问题:由于 FPGA 上的资源是有限的,进行浮点计算可能需要消耗大量的 FPGA 资源,包括 LUT、DSP、BRAM 等。这种资源消耗问题可能会影响系统的可扩展性和可靠性。

最终采用的压缩方式可达到 2:1 的压缩比,同时解压缩单元占用的资源仅 200 余个 LUT、0.5 个 BRAM,详情如下:(2)采用动态分片校正技术将片上内存使用空间缩减至 1/3。

目前FPGA 中多使用4 输入的LUT,所以每一个LUT 可以看成一个有4 位地址线的 的RAM。

因此,逻辑单元是由很多逻辑门构成的更复杂的逻辑电路,它的一个特点是,可以通过设置逻辑单元中逻辑门的不同状态,来改变逻辑单元的逻辑功能。所以,FPGA的“可编程”功能,实际是通过改变逻辑单元中逻辑门的状态来实现的。

FPGA/CPLD在进行逻辑电路设计时,一般使用HDL语言进行输入设计,综合就是把HDL语言转换为综合网表过程。

到此,以上就是小编对于xilinxfpga配置过程的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏