本篇目录:

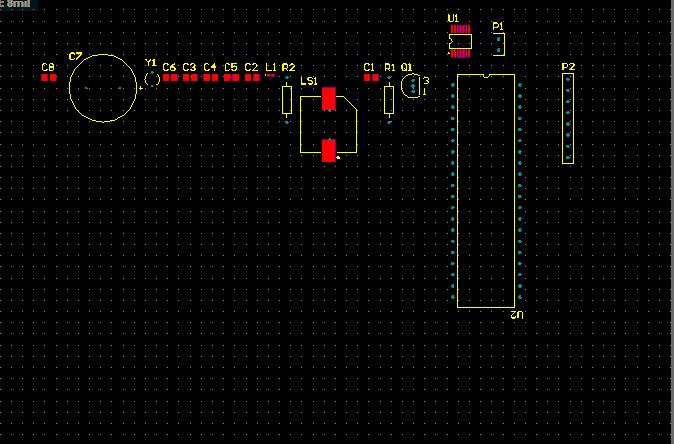

如何用两片7483实现8位二进制加法运算

1、1 1 1 0 只能用半加器来计算最右边一列数:即1加1等于0,进位为1。对于右边第2列数,由于进位的存在,需要加3个数。接下来的几列都有这个问题,每一列二进制位的加法都包括了来自前一列的进位。

2、如果作最低四位的话,可以把C0置0(接地)。74LS283可以进行4位的二进制加法运算,对于无符号整数,可以进行(0~15)+(0~15)的加法运算,和的范围在0~30之间。

3、将图中的电路简化,用下图表示一位全加器。八个一位全加器串联可以组成一个八位全加器,一次可以实现一个字节即八位二进制数的加法运算。楼上的答案是错的。

4、要将一个8位二进制数的最高位和最低位清零,可以将这两位分别设为0,然后将其他位保持不变。这可以通过“与”运算实现。“与”运算的规则是,当两个数的对应位都是1时,结果的对应位才为1,否则为0。

什么是全加器,全减器,半加器,半减器

全加器是能够计算低位进位的二进制加法电路。是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

加法器,是由“全加器、半加器”组成的。(其中的半加器,也可以由全加器代替。)半加器、全加器,都是在二进制数相加时,才会用到的。

全加器是一种电路,它用于在两个数字之间执行加法运算。这是通过将两个数字的每一位分别相加来实现的,并且在需要时进行进位。全加器电路通常由多个半加器单元组成,每个半加器负责处理两个数字的一位。

最简单的全减器是采用本位结果和借位来显示,二进制中是借一当二,所以可以使用两个输出变量的高低电平变化来实现减法运算。

组合逻辑电路的分析流程 与逻辑表示只有在决定事物结果的全部条件具备时,结果才发生。

半加器:只考虑本位相加;全加器:不仅考虑本位相加,而且要考虑低一位的进数进行相加。他们都是针对二进制数的。

详解加法器的电路实现

1、加法器原理及电路图如下:二进制加法1个bit的二进制相加,结果将会是2个bit。多出来的那个bit是进位,就像十进制的两个数相加一样。

2、加法器是一种电路,它可以将两个或多个数字相加。在数字电路中,加法器通常由多个元器件,如逻辑门、寄存器和反馈电路组成。常见的加法器电路包括half-adder(半加器)和full-adder(全加器)。

3、加法器是一种电子电路,它能够将两个或多个数值相加。它通常由几个基本部件组成,包括加法器输入端、进位标志输出端和相应的进位逻辑电路。

到此,以上就是小编对于半加器功能测试原理图及其测试说明的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏