本篇目录:

- 1、英特尔7nm工艺是最佳工艺吗?

- 2、既然已经有机器能够生产5nm芯片,为什么x86不用5nm呢?

- 3、硅基芯片物理极限是七纳米,为何台积电却依然能做出五纳米的芯片?_百度...

- 4、重磅!制程工艺变天,“纳米数字游戏”里的“猫腻”要被终结了

英特尔7nm工艺是最佳工艺吗?

晶体管尺寸:3nm工艺的晶体管尺寸为3纳米,而7nm工艺的晶体管尺寸为7纳米。这意味着3nm工艺的晶体管尺寸更小,有助于提高集成电路的复杂性和性能。

nm不是工艺极限,而是物理极限。要做个小于7nm的器件并不难,大不了用ebeam lith。但是Si晶体管小于7nm,隔不了几层原子,遂穿导致漏电问题就无法忽略,做出来也没法用。

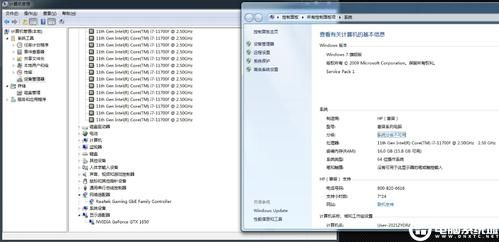

单纯从制作工艺上来说,当然是制造工艺越小越好。 目前Intel系列制作工艺达到了14纳米; AMD系列制作工艺达到了32纳米。 什么是制造工艺: 制造工艺指制造CPU或GPU的制程,或指晶体管门电路的尺寸,单位为纳米(nm)。

nm 制程工艺相比 7nm 制程工艺,拥有高出 18% 的逻辑密度,这意味着在同样的晶体管数量下,列如采用 6nm 制程工艺的天玑 1200 核心面积会更小,将为手机机身提供更大的发挥空间。

密度:7纳米制程相比10纳米制程具有更高的晶体管密度。更小的尺寸意味着在同样的芯片面积上可以容纳更多的晶体管,从而提供更高的集成度和更多的功能。

既然已经有机器能够生产5nm芯片,为什么x86不用5nm呢?

综上所述,以x86指令集架构为代表的英特尔和AMD也想用上5nm的制程技术,但是不能。他们不能像华为、苹果一样成功地去转化台积电的长期积累很多经过流片验证的ARM的IP,所以先进工艺制程之路总会慢一个节拍。

下午好,两种架构和运算模式不同,手机芯片为了降低能耗和体积优选考虑用较小制程配合arm,计算机中央处理器由于有充足电力供应优选较大制程配合x86,同等工艺下后者要明显强于前者很多倍。

芯片最底层的器件就是mos管,特征尺寸越小,制造出的mos管越小,这代表芯片的集成度越高,进而成本降低。在芯片占据相同面积的条件下,集成越高的芯片能够塞入更多的功能电路。

硅基芯片物理极限是七纳米,为何台积电却依然能做出五纳米的芯片?_百度...

在我看来,如果低于2nm,或者是发现到1nm的话,很可能到了极限了。很可能大家不再需求更加低的nm等级了,而是找另外的材料。但是目前来说,还没有比硅更好的、更加适应量产和使用的材料来做半导体。

第一:目前只有台积电才有能力生产5nm芯片的工艺,并且已经能量产。但是他还是使用了美国技术,根据美国新政——要求采用美国技术和设备生产出的芯片,必须先经过美国批准才能出售给华为。

nm就是摩尔极限,也就是说,硅基芯片的极限精度理论上只能达到1nm,但由于自然环境的限制,其实际精度永远不可能达到1nm。制程越小,功耗越小,在实现相同功能的情况下,发热小,电池可使用的时间更长。

芯片的5nm、7nm说白了就是芯片内部晶体管之间的宽度。而数值越小,意味着技术越先进,所以它是很重要的。

为7纳米芯片生产线供应刻蚀机。中微半导体如今通过台积电验证的5纳米刻蚀机,预计能获得比7纳米更大的市场份额。

芯片难度接近理论极限 芯片制造工艺在1995年以后,从500纳米、350纳米、250纳米、180纳米、150纳米、130纳米、90纳米、65纳米、45纳米、32纳米、28纳米、22纳米、14纳米、10纳米、7纳米、5纳米, 一直发展到未来的3纳米 。

重磅!制程工艺变天,“纳米数字游戏”里的“猫腻”要被终结了

1、日前,英特尔CEO帕特·基辛格(Pat Gelsinger)重磅宣布公司有史以来最为详细的制程技术路线图,不仅宣布在2024年进入埃米(ngstrom)时代,还宣布了将以更加科学先进的方式度量制程节点。

到此,以上就是小编对于英特尔处理器是台积电代工吗的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏