本篇目录:

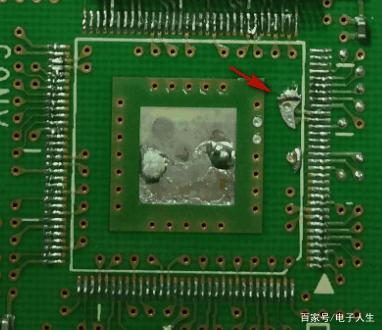

FPGA管脚问题,请看图!

1、\x0d\x0a你的理解是正确的,另外,跨越IO bank的信号没有问题。只是注意跨bank的电平是否一致即可。对于跨IO bank的延迟对于FPGA而言没有多少延迟。

2、实际上就是坐标编号,每一个管脚都有一个唯一的编号,而同一个BANK的编号首字母是相同的。主要是帮助你在程序设计和电路设计时好区分和归类。

3、在FPGA中,有些管脚不会使用到,为了保护FPGA,需要将未使用的管脚状态配置为三态输入或者弱上拉三态输入。

4、在你的程序中用fpga赋值。比如assign z = 0;然后将z分配到你想要设置低电平的引脚,那个引脚就输出低电平了。

5、)采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片。2)FPGA可做其它全定制或半定制ASIC电路的中试样片。3)FPGA内部有丰富的触发器和I/O引脚。

FPGA如何实现别的芯片的管脚连接

1、FPGA的管脚可以支持不同的电平输入输出标准,一般只要其外接芯片的输入输出管脚信号电平不大(一般小于5V)就可以直接连接,但是如果不放心的话也可以在中间加一个电阻,33Ω或者55Ω都可以。

2、配置管脚:MSEL[1:0] 用于选择配置模式,比如AS、PS等。DATA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚。DCLK FPGA串行时钟输出,为配置器件提供串行时钟。nCSO(I/O)FPGA片选信号输出,连接到配置器件的nCS管脚。

3、在系统上电的情况下,通过对PROG引脚置低电子,便可以对FPGA进行重新配置。初始化过程完成后,DONE信号将会变低。(2)清空配置存储器 在完成初始化过程后,器件会将INIT信号置低电平,同时开始清空配置存储器。

FPGA中芯片每个引脚是等同的么?有什么区别没?

管脚是一样的。只是加了N的话,表示为无铅的。对应N的位置还有可能出现的有ES,或者L。

只所以把IO分成几个bank, 是因为FPGA的IO兼容很多单端和双端的IO电平标准,而很多电平标准时参考电压的,在一个bank里大家共享一个参考电压。

同时,fpga支持多次配置(“烧写”),所以就可以在一个板子上不断的调试。空的fpga,什么都不是,所以引脚的定义 什么都不是。只有在烧写后,引脚才有它特定的功能。而且不同的fpga是有不同的引脚。

FPGA的所有管脚用作IO时,是等价的,你不用指定要用固定的那些管脚去接什么器件,只要方便,怎么接都行!只要程序对就可以了。

到此,以上就是小编对于fpga管脚定义的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏