本篇目录:

FPGA如何产生差分信号

1、Xilinx:需要在程序中显性的表示出有2个时钟输入端,在程序内部将这两个差分成对的时钟送入一个IBUFGDS(在ISE 的language assistant中有模板)。

2、一般在FPGA信号处理板中,为了提升信号的抗干扰能力,ADC和FPGA的连接以及FPGA和DAC的连接都使用的是差分接口 在FPGA内部进行信号处理时需要将差分输入转换为单端信号或者将单端信号转换为差分信号输出。

3、fpga差分信号输出可以同时接两个输入。差分传输在两根线上都传输信号,这两个信号的振幅相同,相位相反,在这两根线上的传输的信号就是差分信号。

4、,开发板上除了少数IO端口,比如PROG,JTAG外都是通用IO端口,也就是说可以设置成普通IO,也可以由开发软件管脚约束中配置成差分口。这个要用万用表测相应的IO,看其电压,一般高电平3v表示1,0v表示逻辑0。

5、差分信号的分配始终要先于单端信号。如果某个FPGA提供了片内端接,那么它也可能适用于其他兼容性规则。 在合适的地方分配剩余的信号。在这个阶段,考虑写一个只包含端口分配的HDL文件。

6、如果接收器使用发射时钟,可能会要求延迟从发送端到接收端的时钟信号。有时设计可能需要一个更高的时钟频率来运行FPGA上的逻辑。但是,只有低频率输出的时钟源可以用。

FPGA各个管脚的电压

1、(1)初始化 系统上电后,如果FPGA满足以下条件:Bank2的I/O输出驱动电压Vcc0_2大于lv;器件内部的供电电压Vccint为2.5v,器件便会自动进行初始化。

2、通常XILINX的fpga有三个电压,内核电压,IO电压,和辅助电压。

3、FPGA IO口的电压由IO bank上的VCC引入。一个bank上引入3V TTL电平,那么此时整个bank上输出3V的TTL电平。设置这个第一是为了和current strength一起计算功率。第二个是用于在IO口上加载正确的上拉/下拉电阻。

4、工作电压范围不同:FPGA常用的工作电压范围比单片机的工作电压范围更宽,如FPGA常用的电压范围为2V~3V或8V~5V,而单片机通常工作电压范围为3V~5V或5V。

5、我认为这个问题应该是IO口电平不匹配导致的。FPGA,CPLD(你这块应该是CPLD),电压或功率应该分为两个部分:第一个是核心电压,核心电压是FPGA内部工作时的电压,也就是你用语句生成的电路。一般这个电压比较低。

在做基于FPGA的时间间隔测量时,为什么说时钟频率是100MHZ,所以最大偏...

在FGPA里对时间间隔测量是以时钟的上升沿(或者下降沿)作为计数器的触发信号的,时钟沿的间隔为10ns,所以最大偏差为10ns。时钟频率越高,精度越高。

这个啊,你像下,如果输入的频率的带宽比较大的话,你的校准频率固定的话,就会产生很大的误差了,比如你的校准频率是1MHz的,而输入的是5M的或者更大的,这样的话误差很大的。所以这就是要多点比较好。

时钟信号是一种随时间进行周期性变化的电压信号,一秒钟内变化的周期数就称为频率。一秒钟经过一个周期,频率就是lHz。

改变n和m,即可改变输出信号的频率和相位。若时钟频率 为100MHz,则 。例如取n为1000,m为120,则产生相位为120°,频率为278Hz的正弦信号。当n=1时得最高信号频率为278KHz。

fpga差分对是什么

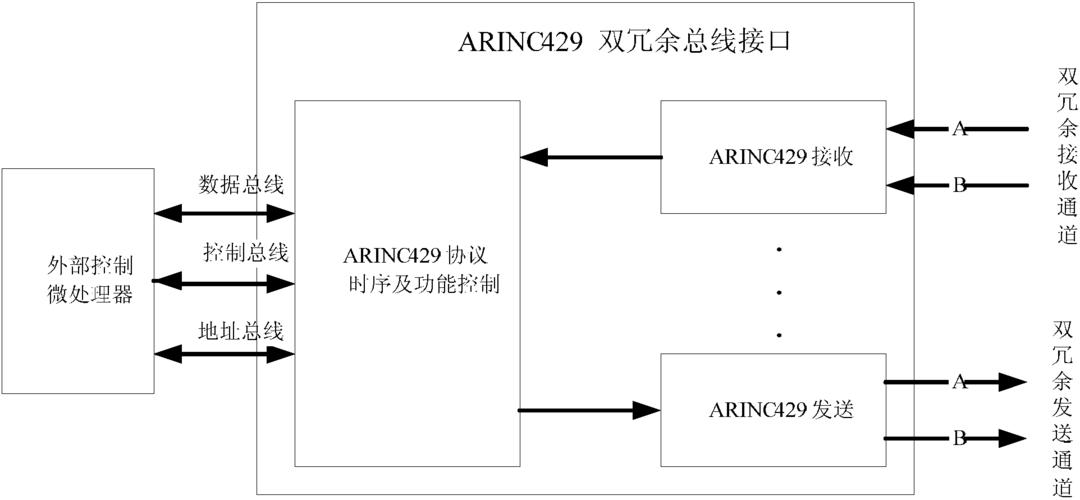

当时钟频率很高时,常采用差分时钟对的输入形式.Xilinx、Altera对差分时钟输入的处理是不同的。Altera仅仅需要一个Pin就可以实现,但必须在管脚约束时指定管脚的电平类型。Xilinx需要两个时钟输入端。

的是pin planner 吧,打开view-pin legend window ,你会看到这些图形代表的含义。Q代表DQ,S是DQS,p,n是差分信号对。角向上的三角形是VCC,向下的是地。

L表示left,R表示right,T表示top,B表示bottom。表示不同的block。

到此,以上就是小编对于fpga输出差分时钟的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏