本篇目录:

- 1、spi和iic技术的应用和比较

- 2、基于SelectIO的高速ADC时序实现(二)

- 3、下面时序图是否是上升沿输入,下降沿输出?为什么我看理解的都是上升沿...

- 4、SPI超详细解析

- 5、请问单片机中的时序有什么用?

- 6、根据spi时序图如何写verilog,谢谢

spi和iic技术的应用和比较

总结:I2C线更少,我觉得比UART、SPI更为强大,但是技术上也更加麻烦些,因为I2C需要有双向IO的支持,而且使用上拉电阻,我觉得抗干扰能力较弱,一般用于同一板卡上芯片之间的通信,较少用于远距离通信。

IN和 data OUT。由于这个原因,采用IIC时CPU的端口占用少,SPI多一根。但是由于IIC的数据线是双向的,所以隔离比较复杂,SPI则比较容易。所以系统内部通信可用IIC,若要与外部通信则最好用SPI带隔离(可以提高抗干扰能力)。

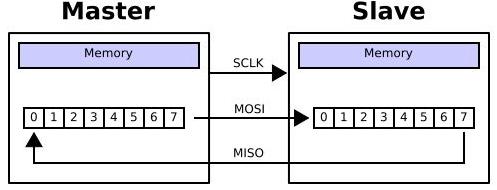

同时,SPI 也没有多主器件协议,必须采用很复杂的软件和外部逻辑来实现多主器件架构。每个从器件需要一个单独的从选择信号。总信号数最终为 n+3 个,其中 n 是总线上从器件的数量。

spi的应用实例: 执行命令时,首先通过SPI串口往Flash发送一连串的数据,然后以命令字开头,除了“读状态寄存器”外,后面还要跟上页地址和页内的字节地址发及一些无关位。

基于SelectIO的高速ADC时序实现(二)

本文通过以高速 ADS42LB69 芯片为例进行实战,利用SelectIO IP快速快速高效完成驱动的生成。关于SelectIO IP的使用,可以参考 Xilinx SelectIO IP使用说明(一) 。

本文通过以高速AD9747芯片为例进行实战,利用SelectIO IP快速高效完成驱动的生成。关于SelectIO IP的使用,可以参考 Xilinx SelectIO IP使用说明(一) 。

在进行模数转换时,转换信号COV_A/B/C用来控制2通道或4通道或6通道ADC进行同时采样。如果将COV_A/B/C3个引脚连接在一起,即6个ADC使用同一转换信号,就可以对6个ADC进行同步采样。

IP核控制ADC自动高速转换的状态机。其作用是实现高速100M的信号采样,就是一个循环的时序控制,让ADC转换一次完成之后由FPGA读出数据并将数据交由第二个IP核(FIFO缓存控制IP),然后立刻读取第二次数据。

下面时序图是否是上升沿输入,下降沿输出?为什么我看理解的都是上升沿...

1、都是上升沿。 SPI 没有 上升沿输入,下降沿输出的 只有 上升沿采集(读写)数据(CPHA=0)跟下降沿采集(读写)数据(CPHA=1)两种模式。

2、上升沿和下降沿判断方法如下:上升沿就是触发的那一瞬间,就是开关闭合的那一瞬间有效,由零变为一的那一下叫上升沿,反之由一变为零的那一瞬间叫下降沿,正常接通以后没有电平变化不起作用。

3、上升沿是指信号电平从低电平向高电平转变的那一段时间。可以理解为信号波形上由低电平开始到高电平结束的这一部分。其中:t1表示信号从低电平开始的时间,t2表示信号达到高电平的时间,T表示上升沿的持续时间。

4、时序图是用来描述数字电路或者控制电路输入和输出端口在不同时间的状态的一种图形,通常用多根水平横线表示多个输入/输出,每根线代表一个输入或输出,通常用“凸起”代表“1”,“平直”代表“0”。

SPI超详细解析

SPI基本概念:SPI=SerialPeripheralInterface,是串行外围设备接口,是一种高速,全双工,同步的通信总线。常规只占用四根线,节约了芯片管脚,PCB的布局省空间。

SPI:高速同步串行口。是一种标准的四线同步双向串行总线。SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。

以下是关于CV、SV、CPI和SPI的常见定义: CV (Cost Variance):成本偏差,用于评估实际成本与计划成本之间的差异。它可以通过以下公式计算:CV = EV (Earned Value) - AC (Actual Cost)。

SPI接口的全称是Serial Peripheral Interface,意为串行外围接口,是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM、FLASH、实时时钟、AD转换器,还有数字信号处理器和数字信号解码器之间。

spi大于1表示什么?进度超前。挣值分析的三个基本参数包括:计划值(PV)、实际成本(AC)和挣值(EV)。四个评价指标包括:进度偏差(SV)、成本偏差(CV)、成本执行指标(CPI)和进度执行指标(SPI)。

请问单片机中的时序有什么用?

单片机时钟是一种用于提供时序和节奏的电子组件,以确保单片机内部的各个部件能够协同工作。单片机时钟的主要功能是产生稳定的时序信号,以控制单片机内部的各种操作。

时序主要是说明逻辑变量(开关量,产生来源:时钟、引脚、寄存器等)的逻辑次序及相互间关系的一个时间参数或是一种表达方法(时序图)。需要了解哪个或哪几个是自变量,哪个或哪几个是因变量。

早期(最经典)的单片机的时序是这样的:■(1)振荡周期:也称时钟周期,是指为单片机提供时钟信号的振荡源的周期,一般实验板上为10592MHZ,12MHZ和24MHZ用的也比较多。

CPU各针脚在时间上的工作关系。时序可以分为两种不同粒度:时钟周期和总线周期。一条指令的执行需要若干个总线周期才能完成。而一个总线周期又由若干个时钟周期组成。CPU在运行过程中是按照统一的时钟一步步执行每一个操纵的。

首先:单片机的ALE PSEN RD WR 都是用来选通器件的。要理解单片机的时序图,必须先弄清指令的执行过程。

简单来说,单片机的时序就是单片机在晶振的时钟频率作用下,其输入和输出端口的电平变化关系。

根据spi时序图如何写verilog,谢谢

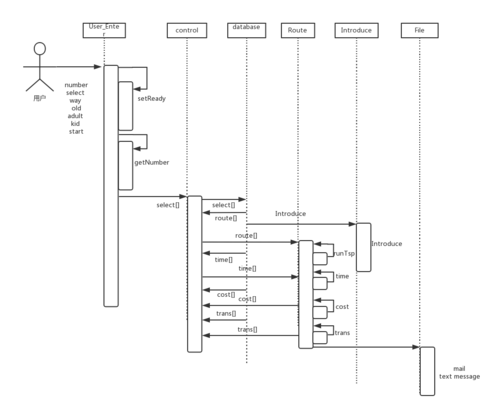

1、时序可以通过状态机实现,将时序分为不同的状态,比如idle,开始,传地址,传数据,结束等等,然后通过不同的条件进行状态转换。这是简单的时序实现,复杂的话,不是这里能说明白的,还是看书吧。

2、按照SPI的时序写驱动程序就可以了,最好事先设计好模块。

3、首先你的题意表达得非常不清楚(DATA没说位数,不知道DATA的输出具体是什么),只根据你这个时序图看,各个信号都是输出(每个信号处都标明有o输出除了WAIT是i输入以外)这明明就是个测试波形,写出的文件就是testbench。

4、你可以把SCL进行8分频、9分频的,这样SCL和BCLK是同步的,识别到SCL沿时,用8个BCLK传输数据即可。建议查看下I2C\I2S\SPI等类似的协议和代码,对于你理解完成Verilog编写代码会有很大帮助和指导的。

5、你的第二个问题。首先,计数器是基于时序逻辑的,所以基本上,count需要是reg型。至于是不是output就看你是否要输出它了。至于你所说的延时问题,由于没有图,所以我猜想你是在time analysis(时序仿真)下得到的结果。

6、用 quartus 10 编译,没啥问题,可以通过。可能你编译用的verilog版本选用2001的试试吧。

到此,以上就是小编对于spi时序图详解的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏