本篇目录:

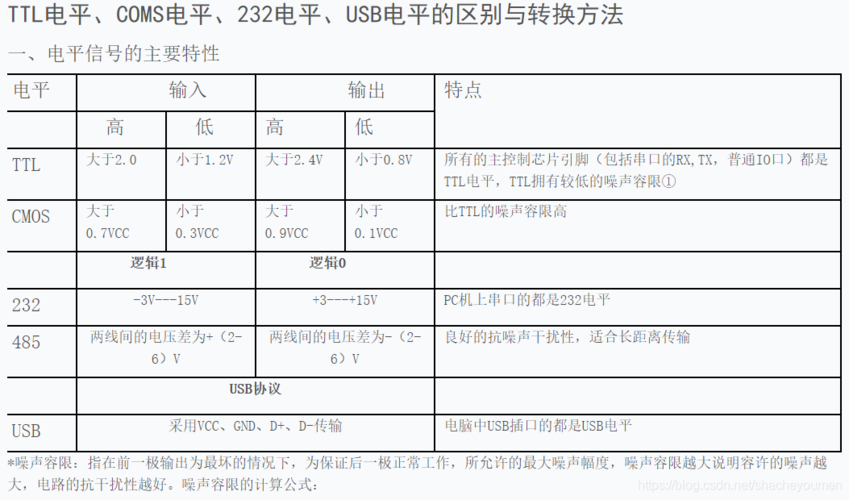

常用逻辑电平标准总结

和上面的GTL相似,输入为输入为比较器结构,比较器一端接参考电平(VCCIO/2),另一端接输入信号。对参考电平要求比较高(1%精度)。

:输入高电平(Vih): 保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高电平。

现在常用的是:TTL数字电路电源是5V,7V 高电平 5V, 0V (=) 低电平 3V。CMOS数字电路电源电压一般是3V--9V, 2/3VCC 高电平 (=) VCC,0V (=) 低电平1/3VCC。

·RS-422/485和RS-232是串口的接口标准,RS-422/485是差分输入输出,RS-232是单端输入输出。一点补充:RS-232C采用的是负逻辑,即逻辑“1”:-5V至-15V; 逻辑“0”:+5V至+15V。

lvcmos33电平标准

1、单端信号接口标准:LVTTL和LVCMOS(JESD8-5,JESD8-B)SSTL(JESD8-8,JESD8-9B,JESD8-15)HSTL(JESD8-6)LVTTL和LVCMOS结构通常是简单的push-pull。

2、有一些相关的规定。1,比如与芯片类型有关,74hcxx输入高低电平分界在0.3-0.7vdd之间,如果电源电压为5v,分界在5v到5v都算合格。

3、LVCMOS:Low VoltageComplementary Metal Oxide Semiconductor。3V LVCMOS:Vcc:3V;VOH=2V;VOL=0.1V;VIH=0V;VIL=0.7V。

FPGA架构的功耗:FPGA功耗

1、FPGA的功耗由两部分组成:动态功耗和静态功耗,信号给电容性节点充电时产生动态功耗。这些电容性节点可以是内部逻辑块、互连架构中的布线导线、外部封装引脚或由芯片输出端驱动的板级迹线。FPGA的总动态功耗是所有电容性节点充电产生的组合功耗。

2、芯片静态功耗,fpga在上电后还未配置时,由晶体管的泄露电流消耗的功耗。设计静态功耗,FPGA配置完成,设计还未启动,维持I/O的静态电流,时钟管理和其它部分电路的静态功耗。

3、FPGA电功耗很大,节能技巧如下:选择基于Flash的FPGA,因为它是真正的单芯片解决方案,无需配置支持,不存在浪涌功耗,而且静态功耗低。

4、相关功率分析工具中。根据电子发烧友查询,FPGA的功率可以在相关功率分析工具中进行查看。这些工具通常会提供关于FPGA功耗的详细报告,包括不同工作模式下的功耗情况。这些工具可以针对FPGA的功耗进行优化,以实现更高效的能源利用。

5、功耗大约9W。根据芯片规模和实际的资源使用率、时钟速率等关系很大,最大的片子和最小的片子可能差一个数量级。要得到准确的功耗需要结合实际的使用型号和工程,用厂商提供的功耗估算软件计算。

6、整个FPGA设计的总功耗由三部分功耗组成: 芯片静态功耗; 设计静态功耗; 设计动态功耗。

CYCLONE2的中文手册

1、Nios Ⅱ嵌入式处理器是ALTERA公司推出的采用哈佛结构、具有32位指令集的第二代片上可编程的软核处理器, 其最大优势和特点是模块化的硬件结构, 以及由此带来的灵活性和可裁减性。

2、强化天赋:Cyclone[飓风]等级要求:11物理伤害:+2x基础伤害技能冷却:-5秒技能描述:Whirlwind伤害提升且冷却时间缩短Vanguard先锋描述:先锋的信条:最好的防御就是进攻。他们的攻击直接,且强力十足。

3、暗黑破坏神2:毁灭之王 装备修改指南 Diablo 2: Lord of Destruction 08 用FPE2000或其他类似修改器,搜索装备耐久度(注:Data Type (bits)中选32)。格式如下:装备最大耐久度,72,装备现在耐久度。

什么是pcml电平?

1、CML电平的信号是差分信号,而LVTTL是单端信号。如果要连接需要弄一堆转换电路。所以基本上认为不得行。CML与LVPECL比较,都可以是用在高速信号上的。

2、(P)ECL是高速领域内一种十分重要的逻辑电路,它的优良特性使它广泛应用于高速计算机、高速计数器、数字通信系统、雷达、测量仪器和频率合成器等方面。 3CML电平 CML电平是所有高速数据接口中最简单的一种。

3、(1)[例] 如果功率P为1mw,折算为dBm后为0dBm。(2)[例] 对于40W的功率,按dBm单位进行折算后的值应为:10lg(40W/1mw)=10lg(40000)=10lg4+110lg10000=46dBm。

4、CML:是内部做好匹配的一种电路,不需再进行匹配。三极管结构,也是差分线,速度能达到3G以上。只能点对点传输。GTL:类似CMOS的一种结构,输入为比较器结构,比较器一端接参考电平,另一端接输入信号。2V电源供电。

5、我们一般常用的是PNP型,即高电平有效状态;NPN很少使用。NPN与PNP中:N是负极的英文第一个字母;P是正极的英文第一个字母。

6、电平,是指两功率或电压之比的对数,有时也可用来表示两电流之比的对数。电平的单位分贝用dB表示。常用的电平有功率电平和电压电平两类,它们各自又可分为绝对电平和相对电平两种。

常用电平标准有哪些?越详细越好,越多越好。

当输入电平高于Vih时,则认为输入高电平;当输入电平低于Vil时,则认为输入低电平。电平的单位分贝用dB表示。常用的电平有功率电平和电压电平两类,它们各自又可分为绝对电平和相对电平两种。

在数字电路中,般规定低电平为0~0.25V,高电平为5~5V。低电平表示0,高电平表示1。

输入小于1/2VCC(电源电压)就是低电平,反之是高电平。实际的器件是做不到的,也不实用,如果输入电压在1/2VCC附近有干扰,就会发生错误的输入信号。

TTL电平信号规定,+5V等价于逻辑“1”,0V等价于逻辑“0”(采用二进制来表示数据时)。这样的数据通信及电平规定方式,被称做TTL(晶体管-晶体管逻辑电平)信号系统。

在逻辑电路中会指定两点或几点电量中的一个为基准(逻辑准位),则比值大于1为高电平,小于1为低电平。简单的说就是高于基准的就是高电平,反之就是低电平。电平是个无因次量(没有单位的物理量)。

规定输出高电平4V,输出低电平0.4V。在室温下,一般输出高电平是5V,输出低电平是0.2V。最小输入高电平和低电平:输入高电平≥0V,输入低电平≤0.8V,噪声容限是0.4V。

到此,以上就是小编对于hta标准的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏